为什么In2O3可以制造0.7 nm原子层薄的晶体管?

诸如铟镓锌氧化物(IGZO)之类的非晶氧化物半导体是用于平板显示应用的薄膜晶体管(TFTs)中的主要沟道材料。最近,氧化物半导体,例如氧化铟(In2O3),氧化铟锡(ITO),W掺杂In2O3(IWO)和IGZO,可以应用于后段制程(BEOL)兼容晶体管中以进行单片3D集成,引起了广泛的研究兴趣。尽管In2O3比四元IGZO具有高得多的电子迁移率,但由于两个原因,IGZO在TFT技术中被采用并商业化,而不是In2O3。首先,In2O3通过溅射沉积形成多晶薄膜,由于晶界而导致电学性能不稳定

研究背景

诸如铟镓锌氧化物(IGZO)之类的非晶氧化物半导体是用于平板显示应用的薄膜晶体管(TFTs)中的主要沟道材料。最近,氧化物半导体,例如氧化铟(In2O3),氧化铟锡(ITO),W掺杂In2O3(IWO)和IGZO,可以应用于后段制程(BEOL)兼容晶体管中以进行单片3D集成,引起了广泛的研究兴趣。尽管In2O3比四元IGZO具有高得多的电子迁移率,但由于两个原因,IGZO在TFT技术中被采用并商业化,而不是In2O3。首先,In2O3通过溅射沉积形成多晶薄膜,由于晶界而导致电学性能不稳定。其次,块材In2O3薄膜的电子密度非常高并且难以控制,因此无法实现增强型操作以抑制零栅极偏置时的截止电流(IOFF)。这两个主要挑战阻碍了In2O3在TFT技术中用于显示应用,并限制了In2O3作为BEOL兼容晶体管沟道的应用。

成果介绍

有鉴于此,近日,美国普渡大学叶培德教授团队利用原子层沉积(ALD)的非晶In2O3沟道(厚度低至0.7 nm)展示了增强型场效应晶体管。研究发现,厚度对In2O3的材料和电子输运至关重要。In2O3在原子尺度的可控厚度使得能够在与常规电介质集成的In2O3沟道中设计足够的2D载流子密度。阈值电压和沟道载流子密度可以通过沟道厚度进行显著调控。这种现象可以利用陷阱中性能级(TNL)模型来理解,其中费米能级趋于在In2O3的导带内部深处排列,并由于量子限制效应而可被调制为原子层薄In2O3的带隙,通过密度函数理论(DFT)计算证实了这一点。增强型非晶In2O3晶体管的演示表明In2O3是BEOL兼容晶体管和单片3D集成应用中具有竞争力的沟道材料。文章以“Why In2O3 Can Make 0.7 nm Atomic Layer Thin Transistors”为题发表在著名期刊Nano Letters上。

图文导读

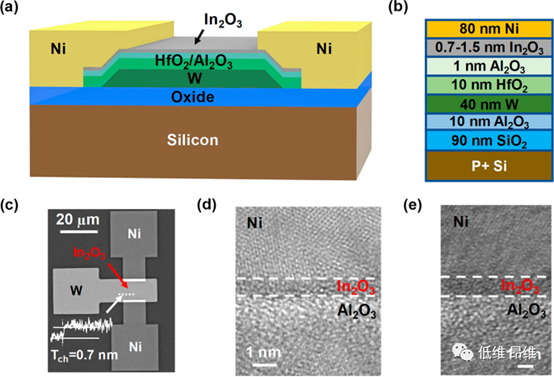

图1. (a)In2O3晶体管的示意图。(b)In2O3晶体管的栅极叠层。(c)沟道厚度为0.7 nm的In2O3晶体管的SEM和AFM测量。(d&e)0.7 nm和1.2 nm厚In2O3的HRTEM横截面图像。

图1a给出了在Si衬底上制造的背栅In2O3 TFT的示意图。图1b显示了具有详细层厚度的栅极堆叠,包括40 nm W作为栅极金属,10 nm HfO2和1 nm Al2O3作为栅极电介质,0.7-1.5 nm In2O3作为半导体沟道以及80 nm Ni作为源极/漏极(S/D)欧姆接触。1 nm Al2O3用于在加工过程中保护HfO2并改善界面质量。图1c给出了In2O3晶体管的SEM图像,其中沟道厚度Tch为0.7 nm。图1d和e分别显示了0.7和1.2

nm厚In2O3的HRTEM横截面图,表明ALD制备的纳米级In2O3超薄薄膜是非晶态的,这与通过溅射沉积的块材多晶In2O3薄膜有很大不同。这种无定形性质很可能源自厚度依赖的结晶度,已在各种氧化物中广泛报道。

图2. 具有不同沟道厚度的In2O3晶体管的ID-VGS和ID-VDS特性。

图2a给出了沟道长度(Lch)为0.2 μm,Tch为0.7 nm的In2O3晶体管的ID-VGS特性,其开/关比超过107并且VT为4.9 V。In2O3沟道在垂直方向仅由几个原子组成,并且具有8.9的低介电常数,这进一步增强了栅极静电控制。超薄沟道和低介电常数特性可以提高针对超大规模BEOL逻辑应用的短沟道效应的抗扰性。Lch为0.2 μm,Tch为0.7 nm的In2O3晶体管的ID-VDS特性如图2b所示,在VDS=4 V时,最大漏极电流为0.5 μA/μm。图2c给出了Lch为0.2 μm,Tch为1 nm的In2O3晶体管的ID-VGS特性,开/关比超过109并且VT为3.0 V。还可以使用1 nm厚的In2O3沟道实现增强型操作。相应的ID-VDS曲线如图2d所示,在VDS=3 V时,最大漏极电流提高到96 μA/μm。图2e给出了Lch为0.2 μm,Tch为1.2 nm的In2O3晶体管的ID-VGS特性,开/关比超过1010并且VT为0.3 V。ID-VDS特性如图2f所示,在VDS=1.2 V时,最大漏极电流为503 μA/μm。图2g展示了Lch为0.2 μm,Tch为1.5 nm的In2O3晶体管的ID-VGS特性,开/关比超过107并且VT为-3.8 V。ID-VDS特性如图2h所示,在VDS=1 V时,最大漏极电流为1 mA/μm。所有这些器件性能都是薄膜晶体管技术中最好的,不包括其原子薄沟道和进一步缩放带来的潜在增强。

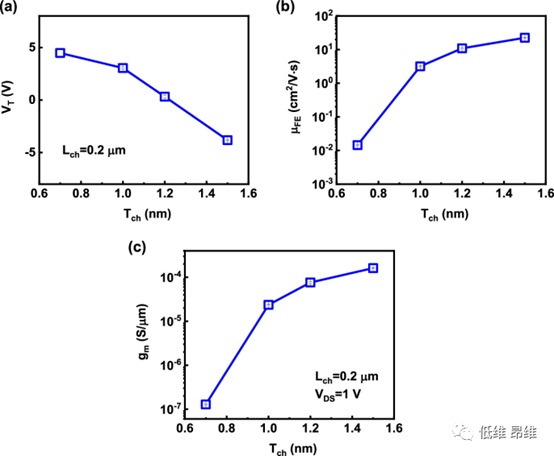

图3. 沟道长度为0.2 μm的In2O3 MOSFET的阈值电压,场效应迁移率和跨导与沟道厚度的关系。

可以看出,超薄In2O3中的电子输运与块材In2O3有很大不同。厚度依赖的电子输运特性在图3中进行了统计研究。非常小的标准偏差证实了ALD生长的In2O3具有高度均匀性。图3a显示了Lch=0.2 μm的In2O3晶体管的厚度依赖性VT。随着Tch从0.7 nm增加到1.5 nm,VT从4.5 V变为-3.8 V。增强型和耗尽型都可以通过Tch控制来实现。厚度依赖的场效应迁移率(μFE)如图3b所示,μFE随Tch呈指数下降,表明在原子薄In2O3薄膜中更强的无序引起的EC电势波动和电子散射。图3c给出了In2O3晶体管在VDS=1 V时gm与Tch的关系。由于较高的迁移率,gm随Tch增加而增加,在1.5 nm Tch处实现的最大gm为162 μS/μm。

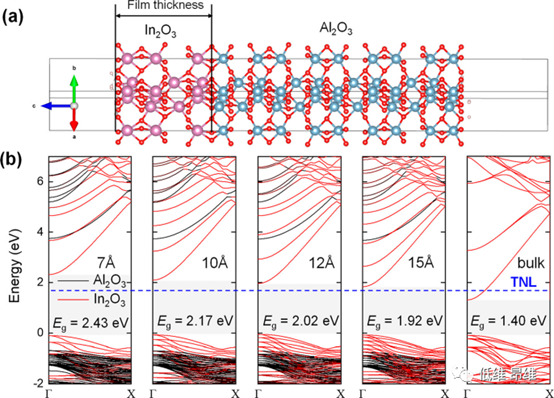

图4. (a)DFT计算中使用的In2O3薄膜的原子结构。(b)不同厚度In2O3薄膜沿Γ到X方向计算的能带结构。

为什么突然可以将3D半导体沟道缩小到0.7-1.5 nm的原子层厚度,与2D 范德华材料单层或双层的厚度相当,并且比传统3D半导体(例如Si和GaAs)的极限厚度薄得多?费米级钉扎概念在半导体材料和器件开发中非常重要,并且已经开发了各种模型。由于界面的物理和化学非常复杂,因此对于金属/半导体和半导体/电介质界面都没有全面的模型。电荷中性能级(CNL)模型被广泛用于描述金属/半导体界面。同时,可以使用所谓的陷阱中性能级(TNL)来描述所有在具有ALD电介质的III-V和Ge中的实验观察。更有趣的是,所有块材半导体中的能级及其CNL,TNL甚至缺陷能级的排列最终都具有很强的相关性。

首先,块材In2O3中的CNL位于EC之上约0.4 eV,因此厚的In2O3薄膜被认为是导电氧化物。在半导体/电介质界面处,EF在In2O3中的位置由TNL确定。与CNL相似,如果In2O3沟道为1.5 nm或更厚,则In2O3/Al2O3界面处的TNL也将在EC上方对齐,并且只有较厚的沟道才能实现耗尽型操作。常规的高k电介质只能调制高达2-3×1013/cm2的载流子密度,因此如果沟道的厚度大于2 nm,则沟道不会耗尽。因此,如果不施加栅极电压,则对于厚的In2O3薄膜,EF高于EC,而对于较薄的In2O3薄膜,在原子层尺度上,EF值低于EC。图3a中厚度依赖的VT清楚地表明了这种趋势。一旦沟道厚度比1 nm薄得多,In2O3中的TNL就会移动到EC之下很深的位置。

可以通过量子限制效应来理解厚度控制的TNL排列,就像2D范德华材料中层数依赖的能带结构一样。在图1a所示的晶体管结构中,半导体In2O3被绝缘的Al2O3和空气夹在中间,因此In2O3中的电子输运就像在无限量子阱中的2D电子气一样。由于量子限制效应,EC的变化就像无限势阱中电子的基态能量一样。为了验证这种机制,进行了DFT模拟以研究EC如何随In2O3厚度变化。DFT模型由堆积在一层刚玉Al2O3层上的刚玉型In2O3层(代表非晶In2O3层)组成,如图4a所示。对于ALD生长的In2O3薄膜,其表面会自然地被-OH基团终止,因此用H原子终止In2O3表面是合理的。In2O3/Al2O3界面处的大导带偏移(>4 eV)保证了足够高的势垒,可在In2O3层上引入量子限制效应。沿Γ-X方向计算的厚度依赖的能带结构如图4b所示。当In2O3厚度减小时,尽管EV几乎保持不变,但EC的绝对能级上升,这清楚地表明了超薄In2O3薄膜中厚度依赖的量子限制效应。随着In2O3厚度进一步减小,TNL会朝着中间带隙连续向下移动。因此,在降低Tch的同时,TNL向带隙内部移动更深,从而导致载流子密度降低和正VT漂移减小。

总结与展望

本文研究发现薄膜厚度对3D半导体In2O3的材料和电子输运性能至关重要。通过ALD实现的低至0.7 nm的超薄In2O3克服了In2O3

TFT技术中的两个主要挑战,即非晶相和沟道中过高的载流子密度。通过量子限制效应可以理解强的厚度依赖性电子输运。DFT计算结果也与实验数据吻合良好。高性能增强型非晶In2O3晶体管的演示表明,In2O3是显示应用和BEOL兼容晶体管应用中具有竞争力的沟道材料。