什么是二进制加法器和减法器

在数字电路中,二进制加法器和减法器用于对二进制数字进行加法和减法。这个电路的操作主要取决于二进制值。这里,电路中的控制信号保持二进制值。这是。。。

在数字电路中,二进制加法器和减法器用于对二进制数字进行加法和减法。这个电路的操作主要取决于二进制值。这里,电路中的控制信号保持二进制值。它是算术逻辑单元的组成部分之一。该电路需要关于半加器、全加器、二进制加法和减法的先决条件信息。同时,还可以设计用于执行加法和减法的电路。本文讨论了二进制加法器和二进制减法器的概述。

二进制加法器和减法器

二进制加法器和减法器概述主要讨论二进制加法电路、二进制加法器(半加法器和全加法器)、并行二进制加法器、二进制减法电路、二进制减法器(半减法器和全减法器)和并行二进制减法器。

二进制加法电路

在数字电路中,二进制加法的算术运算可以使用逻辑门来执行。为此,使用了一个双输入逻辑门,它与OR门略有不同。“或”门将两个整数相加,并在两个输入为1时生成一个输出。但是,当我们将“或”门与“异或”门进行比较时,由于单独的操作,它无法实现二进制加法。在包含“或”门中,它包括三个o/ps,将它们相加以生成总和。现在,我们可以将这两个门相互比较。

这两个逻辑门之间的主要区别主要包括OR门执行整数的加法,而Ex OR门执行二进制运算。

什么是二进制加法器?

二进制加法器是一种主要用于执行两个二进制数的算术运算(如加法)的数字电路。二进制加法器可以通过将它们串联而设计为具有全加法器电路。第一全加法器的输出进位连接到第二全加法器的输入。这些电路分为半加法器、全加法器和并行加法器。

半加法器

半加法器是一种用于对两个二进制数进行加法运算的电子电路。半加法器将两个二进制数字相加,生成两个输出,如输出和进位。半加法器的输入是A和B,而输出是和和进位。一般表示使用逻辑门,如AND门和XOR逻辑门。

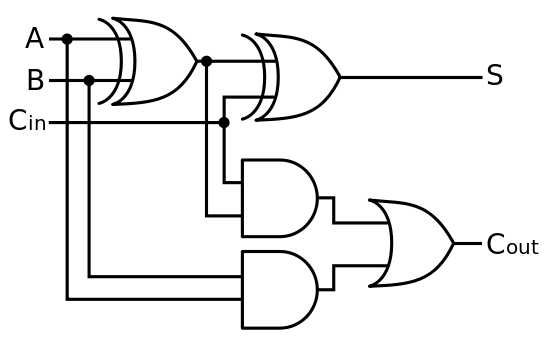

完整加法器

全加器是一种用于对三个二进制数进行加法运算的电子电路。全加法器将三个二进制数字相加,生成两个输出,如输出和进位。半加法器的输入是A、B和Cin,而输出是sum和Cout。全加法器是两个半加法器的组合,其中像AND和XOR门这样的逻辑门通过OR门连接。请参阅此链接了解更多关于半加法器和全加法器的信息。

并行二进制加法器

并行二进制加法器是由各种并联的全加法器设计的组合电路。在并行二进制加法器中,全加法器的数量主要取决于加法中的位数。

并行二进制加法器的设计可以使用逻辑门来完成。逻辑电路中的相关模块将看起来像两个加法器的逻辑电路,如半加法器和全加法器。

二进制减法电路

减法是一种算术函数,将一个数字从另一个数字中减去以获得相等的数量。要从中减去另一个数字的数字被称为被减数。类似地,从被减数中减去的数被称为减数。与二进制加法相同,这也包括4种可行的替代运算,其中每个被减数位都可以从被减数位中减去。

然而,在第二条规则中,被减数的比特比减数的比特小,因此1被借用来完成减法。与加法器电路相关,这些电路也分为半减法器、全减法器和并行减法器。

半减法器

类似于半减法器的组合逻辑电路用于减去两个单比特数字。它包括两个输入和两个输出。输入是A、B,而输出是借位和差值。请参阅此链接了解更多关于Half减法器的信息。

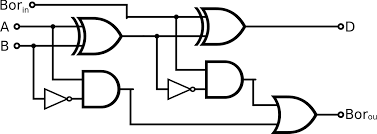

全减法器

类似于半减法器的组合逻辑电路用于减去两个单比特数字。它包括三个输入和两个输出。输入为A、B和Bin,而输出为Borrow&Difference。请参阅此链接以了解有关Full减法器的更多信息。因此,该减法器包括通过考虑低有效级中的借位来执行三位减法的能力。请参阅此链接以了解有关Full减法器的更多信息。

并行二进制减法器

并行二进制减法器是一种数字电路,用于通过对并行内的等效位对进行运算,找出长度内优于另一位的两个二进制数的差。这个减法器的设计可以通过多种方式完成,比如减法器和所有使用减数补码输入的全减法器的组合。

因此,这一切都是关于二进制加法器和减法器的,包括二进制加法电路、类似半加法器和全加法器的二进制加法器、并行二进制加法器、二进制减法电路、类似半减器和全减法器的二进制减法器以及并行二进制减法器。这里有一个问题,什么是并行加法器/减法器?