Cadence称赞EDA 2.0具有统一的数据和人工智能驱动的验证

Cadence Design Systems推出了一个数据平台,该平台可以收集EDA工具收集的大量数据,并利用该平台实现一套人工智能驱动的验证应用程序,旨在提高覆盖率,加快复杂片上系统(SoC)设计缺陷的根本原因分析。 其新的联合企业数据和...

Cadence Design Systems推出了一个数据平台,该平台可以收集EDA工具收集的大量数据,并利用该平台实现一套人工智能驱动的验证应用程序,旨在提高覆盖率,加快复杂片上系统(SoC)设计缺陷的根本原因分析。

其新的联合企业数据和人工智能(JedAI)平台使工程师能够从大量芯片设计和验证数据中获得“可操作的智能”,为新一代人工智能驱动的设计和验证工具打开了大门,这些工具将有助于提高生产力、功率、性能和面积(PPA)。Cadence表示,这将导致从EDA中的单次运行、单引擎算法向利用大数据和人工智能优化整个SoC设计和验证流程中多个引擎的多次运行的算法的代际转变。

基于这个JedAI平台,该公司还宣布了其CadenceVerisium验证平台,一套应用程序,使用JedAI的大数据分析功能来优化验证工作负载,该应用程序与Cadence验证引擎本地集成。通过部署Verisium,所有验证数据,包括波形、覆盖率、报告和日志文件,都汇集在JedAI中。建立了机器学习(ML)模型,并从这些数据中挖掘出其他专有指标,以大幅提高验证生产率。Cadence表示,JedAI平台能够将其在Verisium验证中的数据和人工智能计算软件创新与Cadence的Cerebrus Intelligent Chip Explorer的实现和Optimity Intelligent System Explorer的系统分析相统一。

自动化EDA工具的数据分析

Cadence的营销总监Moshik Rubin在德国慕尼黑的一次发布会上解释了新平台的重要性,他称赞该公司新的人工智能驱动的数据平台和验证套件是EDA 2.0的出现。他表示,SoC越来越大、越来越复杂,集成了数百个IP。随着这些IP块的发展和改进,每个IP块都在不断变化,手动关联不同的结果和测试失败变得越来越困难。确定故障的根本原因可能需要数十名工程师和数周时间。

这就是通过人工智能驱动的平台实现数据分析自动化的地方,可以帮助缩短验证和调试时间,还可以减少所需的工程师数量。Cadence JedAI平台旨在更容易管理与消费者、超大规模计算、5G通信、汽车和移动应用程序相关的设计复杂性。使用Cadence模拟/数字/PCB实现、验证和分析软件的客户,甚至第三方应用程序,都可以使用JedAI平台来统一和分析他们的所有大数据。该平台支持云计算,在领先的云提供商的安全设计环境中提供可扩展的计算资源。

Moor Insights&Strategy首席执行官、创始人兼首席分析师Pat Moorhead表示, “为了使半导体行业能够继续保持强劲的增长轨迹,芯片设计过程变得更加高效以跟上市场需求至关重要。通过人工智能和大数据分析改进设计过程为工程团队带来了明显的好处,他们现在可以从指尖的大量EDA数据中提取关键知识新的Cadence JedAI平台旨在为用户提供自动化、智能的设计见解,以及大幅提高工程团队生产力的能力。”

Cadence人工智能研发副总裁Venkat Thanvantri补充道, “以前,我们看到,一旦芯片设计项目完成,宝贵的数据就会被删除,为下一个项目让路。遗留数据中有宝贵的经验教训,Cadence JedAI平台使工程团队能够轻松访问这些经验教训,并将其应用于未来的设计,以提供最佳的工程生产率和PPA,最终更可预测、更高高质量的产品成果。”

<img data-lazy-fallback="1" decoding="async" src="https://uploads.9icnet.com/images/aritcle/20230517/Cadence-verification-chart.png" alt="Cadence verification chart" class="wp-image-4476343" width="602" height="330" srcset="https://uploads.9icnet.com/images/aritcle/20230517/Cadence-verification-chart.png 602w, https://uploads.9icnet.com/images/aritcle/20230517/Cadence-verification-chart.png?resize=300,164 300w" sizes="(max-width: 602px) 100vw, 602px">

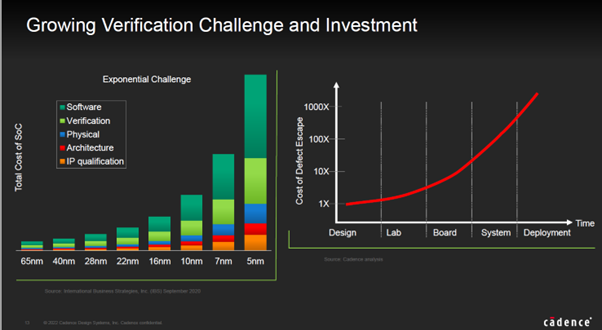

随着SoC复杂性的不断上升,验证成为系统上市的关键途径,通常比任何其他硅工程任务消耗更多的计算和人力资源。(图片:Cadence)

根据鲁宾的说法,验证正在成为设计周期的一个重要组成部分。随着SoC复杂性的不断上升,验证成为系统上市的关键途径,通常比任何其他硅工程任务消耗更多的计算和人力资源。他告诉embedded.com,这就是Cadence将调试作为JedAI平台的第一个应用程序的原因。他说,“调试是RoI最高的用例。主要挑战是找到正确的数据集。”他还说,由于验证工程师短缺,具有人工智能驱动分析能力的Verisium平台通过提供“机器人工程师”有效地帮助缓解了这一问题。

他补充道。“这将导致验证工程师工作方式的范式转变。”

Cadence在发布会上发布了联发科、三星电子、意法半导体和索尼的一些客户背书。三星电子公司副总裁S.Brian Choi表示, “随着SoC复杂性的不断增长,SoC级验证已成为我们tapeout计划中的一个限速步骤。我们看到了利用人工智能和大数据大幅提高设计和验证生产力的大好机会。我们正在与Cadence密切合作,在我们的移动SoC设计上部署Verisium平台,并已经看到了令人印象深刻的结果nd根本原因错误。”

与此同时,意法半导体STM32数字验证经理Mirella Negro Marcigaglia表示, “为了解决STM32微控制器中IP和SoC设计快速增长的复杂性,功能验证仍然是一个主要问题。Cadence的数据驱动功能验证平台和利用人工智能技术的应用程序是遏制这一问题的一种非常有前途的方法。我们已经观察到,利用Verisium AutoTriage、SemanticDiff和WaveMiner。使用Verisium应用程序和Cadence JedAI平台,我们的目标是在IP和SoC设计中快速实现对bug的测试和本地化,从而大幅提高生产力。”

Verisium应用程序

Verisium平台中提供的初始应用套件:

Verisium验证平台是Cadence验证全流程的一部分,包括Palladium Z2仿真、Protium X2原型设计、Xcelium仿真、Jasper正式验证平台和氦™ 虚拟和混合工作室。请访问。