SYZYGY:基于FPGA的系统的Goldilocks连接标准

我们都知道一个叫金发姑娘的小女孩的故事,她是一个不守规矩的恶棍,闯入一个毫无戒心的家庭,肆意品尝她在那里发现的三碗粥。由于有点挑剔,她认为她舀进嘴里的第一个太烫了;下一个太冷了;但第三个碗刚好好,所以她狼吞虎咽地吃完了。 到目前为止,在将外...

我们都知道一个叫金发姑娘的小女孩的故事,她是一个不守规矩的恶棍,闯入一个毫无戒心的家庭,肆意品尝她在那里发现的三碗粥。由于有点挑剔,她认为她舀进嘴里的第一个太烫了;下一个太冷了;但第三个碗刚好好,所以她狼吞虎咽地吃完了。

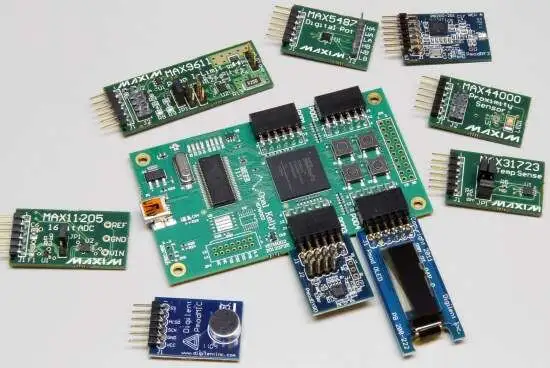

到目前为止,在将外围设备连接到FPGA系统方面,FPGA领域只有极冷和极热的选择。在天平的一端,我们有Digilent的Pmod标准,非常适合1到50MHz范围内的低速外围设备。6针和12针连接器的实现成本低廉,外围设备的成本约为8至50美元,其中有许多现成的产品。

<img data-lazy-fallback="1" decoding="async" alt="" src="https://uploads.9icnet.com/images/aritcle/20230509/media-1246327-max-0289-emb-syz-01.jpg">

(资料来源:Opal Kelly)

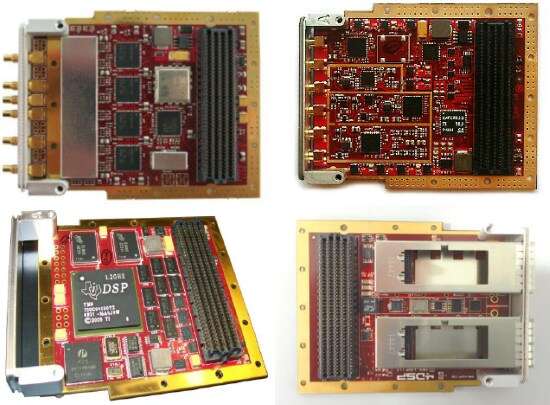

在光谱的另一端,我们发现ANSI/VITA标准被称为FMC(FPGA夹层卡),更适用于数据速率高达10Gbps的高性能外围设备。在这种情况下,72针和200针连接器要贵得多,外围设备本身的成本可能从几百美元到数千美元不等。

<img data-lazy-fallback="1" decoding="async" alt="" src="https://uploads.9icnet.com/images/aritcle/20230509/media-1246324-max-0289-emb-syz-02.jpg">

(资料来源:Opal Kelly)

那么,如果你对一个引脚和性能要求介于Pmod和FMC提供的功能之间的外围板有一个绝妙的想法,你会怎么做?当然,有各种令人难以置信的连接解决方案可供选择,但随机选择连接器与使用可与其他供应商的各种系统配合使用的标准解决方案之间有着天壤之别。

所有这些都把我们带到了蛋白石凯利,以提供一系列功能强大的基于USB和PCI Express FPGA的集成模块而闻名,这些集成模块将在FPGA中实现的用户硬件设计连接到在PC上实现的用户软件。例如,在USB的情况下,Opal Kelly处理所有这些烦人的小细节,如枚举过程、低级驱动程序,和总线超时(你可以通过阅读了解这一切是如何结合在一起的本栏我前段时间写的)。

一段时间以来,Opal Kelly的客户一直在抱怨Pmod和FMC域之间没有良好的标准连接解决方案。为了解决这个“漏洞”,Opal Kelly的同事们刚刚宣布发布SYZYGY,这是一种将高性能外围设备连接到FPGA硬件的新的开放标准。

顺便说一句,“syzygy”是一个真实的词——这是一个天文学术语,指的是在日食或月食期间排列的三个天体,如太阳、月亮和地球(见我的第一次日全食太棒了!)

SYZYGY旨在满足FPGA和通用硬件外围设备之间对紧凑、低成本、低引脚数、高性能连接解决方案的需求。高速数据采集、数字图像采集、软件无线电和数字通信设备是SYZYGY开发的主要灵感来源。

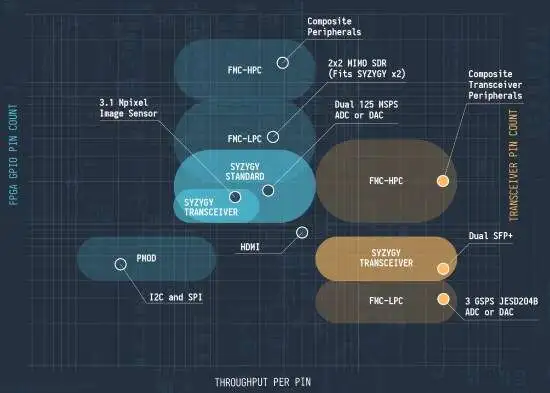

SYZYGY规范定义了两种连接器类型:Standard(标准)和Transceiver(收发器)。标准SYZYGY连接器提供多达28个单端阻抗控制信号,其中16个可以定义为LVDS等接口标准的差分对。收发器SYZYGY连接器拥有四条千兆级收发器连接通道,还提供多达18个单端信号。收发器连接器用于JESD204B数据采集、SFP+收发器和其他需要高速SERDES的设备。标准连接器和收发器连接器都有可选的低成本、高性能同轴或双轴电缆组件。

<img data-lazy-fallback="1" decoding="async" alt="" src="https://uploads.9icnet.com/images/aritcle/20230509/media-1246328-max-0289-emb-syz-03.jpg">

GPIO(蓝色)和收发器(橙色)解决方案(来源:Opal Kelly)

正如我们所看到的,SYZYGY的“最佳点”位于Pmod和FMC之间。SYZYGY无意取代或取代Pmod或FMC;对于低引脚数、低速、廉价的外围设备,Pmod仍然是一条路要走;对于高引脚数、极端性能、高成本的外围设备,FMC可能是最佳选择;但是,如果您需要适中的引脚数量,再加上高性能和低解决方案成本,那么SYZYGY将给您带来微笑。

SYZYGY设计用于适应FPGA系统常见的各种I/O电压,定义了SYZYGY-DNA和SmartVIO。SYZYGY-DNA是外围设备将个性数据(如制造商名称、产品名称和序列号)通信到载体的一种简单方式。SmartVIO包含在DNA有效载荷中,并定义外围设备可接受的I/O电压范围,以便载波可以相应地设置I/O电压。

为了让用户能够评估这一新标准,Opal Kelly提供了一种基于FPGA的开源SYZYGY兼容载体,称为SYZYGY Hub。

<img data-lazy-fallback="1" decoding="async" alt="" src="https://uploads.9icnet.com/images/aritcle/20230509/media-1246325-max-0289-emb-syz-04.jpg">

SYZYGY集线器(来源:Opal Kelly)

SYZYGY集线器提供三个标准SYZYGY端口、一个收发器SYZYGY接口、SmartVIO电源传输、一个带Linux操作系统的Xilinx Zynq SoC FPGA、1 Gb以太网、1 GiB DDR3-800、USB Type-C(主机和设备模式)、USB串行UART(控制台访问)和5V至18V电源输入。

Opal Kelly提供SYZYGY作为一种开放标准,运营商和外围设备制造商可以免费获得许可。这种许可方法旨在鼓励一致性、扩散和健康的生态系统,邀请运营商和外围设备制造商、半导体设备制造商、教育机构和研究组织开发自己的附加产品。

欲了解更多信息或下载SYZYGY标准,请访问SYZYGYfpga.io公司