PISO移位寄存器:工作、电路、时序图、Verilog代码及其应用

我们知道触发器用于存储单个二进制数据位,但如果我们想存储多个数据位,则需要几个FF。因此,移位寄存器包括一组FF,用于通过连接多个数据位来存储它们。。。

我们知道触发器用于存储单个二进制数据位,但如果我们想存储多个数据位,则需要几个FF。因此,移位寄存器包括一组FF,用于通过串行连接来存储多个数据位。存储在这些寄存器中的数据可以通过使用CLK信号来移位。用于将数据位向左移位的移位寄存器被称为SLR或向左移位寄存器,而被移位到右侧的数据位被称为SRR或向右移位寄存器。我们知道这些寄存器分为不同的类型,如SISO、SIPO、PISO和PIPO。因此,本文讨论了PISO移位寄存器这被称为串行输出移位寄存器中的并行。

什么是PISO移位寄存器?

使用并行输入并产生串行输出的移位寄存器被称为并行输入串行输出移位寄存器或PISO移位寄存器。该移位寄存器以与SIPO移位寄存器相反的方式工作。在这种类型的移位寄存器中,输入数据以并行方式输入,然后串行输出。因此,第二个FF的i/p是第一个触发器的o/p。

PISO移位寄存器电路图

PISO移位寄存器电路图如下所示。该电路主要包括4个D FF,它们按照图示进行连接。CLK i/p信号直接连接到所有FF,然而i/p数据单独连接到每个触发器。

先前的FF的o/p以及并行输入数据简单地连接到第二触发器的i/p。因此,电路中的FF彼此同步,因为每个触发器都有类似的CLK信号。

PISO移位寄存器工作

在上述PISO移位寄存器电路中,输入数据从D施加到移位寄存器的输入引脚<sub>A.至DD同时之后,在每个CLK周期上从输入引脚一次串行地从移位寄存器读出1位。这里,一个CLK脉冲足以加载4位数据,但需要四个脉冲来卸载所有四位。

在这种并行输入串行输出(PISO)移位寄存器电路中,使用了逻辑门。一个控制信号(Shift/Load)用于控制并行输入和串行输出。之后,非门输出连接到“G1”、“G2”和“G3”,G1、G2和G3的其他输入是B、C和D。这里,“A”直接连接到第一触发器的DA。

直接控制信号连接到‘G4’、‘G5’和‘G6’的一个输入端,‘G4’,‘G5”和‘G6”的另一个输入连接到像QA、QB和QC这样的触发器的输出端。OR门连接到第二、第三和第四触发器的输入,如DBDC和DD所有触发器将连接在单个CLK脉冲中,并且FF输出将在串行数据输出中。

现在我们来看看数据是如何加载的。这里,我们将输入数据选择为1101,然后A=1,B=1,C=0&D=1。当施加到非门的控制信号为“0”时,其o/p将变为“1”,“G1”、“G2”和“G3”将启用,“G4”、“G5”和“G6”将禁用。因此,所有输入都被加载,之后OR门也被启用,数据将被加载到每个触发器的输入。

现在我们将控制信号“1”施加到非门,然后该门的输出将变为“0”,然后G4、G5和G6被启用。一旦CLK脉冲被施加到FF,则数据‘1101’从一个OR门向右移位到另一个。

PISO移位寄存器真值表如下所示。

现在施加的控制信号是“0”,那么要加载的数据和数据将变为1101。

| DA. |

DB | DC | DD |

| 1. | 1. | 0 | 1. |

现在施加的控制信号是“1”,施加CLK脉冲“1”然后数据像Q一样移位A.变为“1”,QB变为“1”,QC变为“0”和QD变为“1”,如下表所示。

| CLK脉冲 | QA. | QB | Qc | QD(数据输出) |

| 0 |

0 | 0 | 0 | 0 |

| 1. |

1. | 1. | 0 | 1. |

| 2. |

0 | 1. | 1. | 0 |

| 3. | 0 | 0 | 1. | 1. |

| 4. | 0 | 0 | 0 | 1. |

如果施加CLK脉冲“2”,则数据像Q一样移位A.变为“0”,QB变为“1”,QC变为“1”和QD变为“0”,如下表所示。

如果施加CLK脉冲“3”,则数据像Q一样移位A.变为“0”,QB变为“0”,QC变为“1”和QD变为“1”,如下表所示。

如果施加CLK脉冲“4”,则数据像Q一样移位A.变为“0”,QB变为“0”,QC变为“0”和QD变为“1”,如下表所示。

PISO移位寄存器时序图

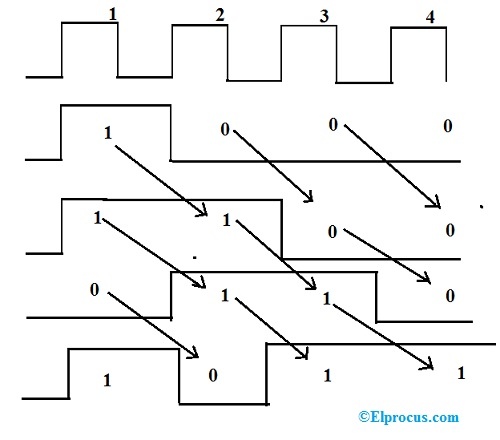

PISO移位寄存器的时序图如下所示。这里我们使用的是一个正边缘CLK i/p信号。一旦施加CLK脉冲,则所有数据都将从Q移位A.QBQC&问D在第二个CLK脉冲之后,“1”移动到图中所示的第三和第四CLK脉冲。因此,在第四CLK之后输出的最终数据将是1011。

Verilog代码

这个PISO移位寄存器的verilog代码r如下所示。

模块Shiftregister_PISO(Clk、Parallel_In、load、Serial_Out);

输入Clk,负载;

输入[3:0]并行_In;

输出reg Serial_Out;

注册[3:0]tmp;

始终@(posedge Clk)

开始

if(负载)

tmp<=并行_In;

其他的

开始

串行输出<=tmp[3];

tmp<={tmp[2:0],1'b0};

终止

终止

末端模块

应用

aPISO移位寄存器的应用包括以下内容。

- PISO移位寄存器用于将数据从并行形式更改为串行形式。

- 这种移位寄存器用于为数字电路产生时间延迟。

- PISO移位寄存器的实际应用是在几个引脚上将大量开关闭合读取到芯片中。

- 这个寄存器将数据读入存储器芯片。

因此,本文概述了PISO移位寄存器的工作原理及其应用。最常用的PISO移位寄存器IC有:;74HC165 IC、74HC164 IC、74674 IC和74HC595 IC。这里有一个问题,什么是SISO移位寄存器?