PMOS晶体管:工作、制造、截面及其特性

MOS晶体管是大规模集成电路设计中最基本的元件。这些晶体管通常分为PMOS和NMOS两种类型。NMOS和PMOS晶体管的组合被称为CMOS晶体管。。。。

MOS晶体管是大规模集成电路设计中最基本的元件。这些晶体管通常分为PMOS和NMOS两种类型。NMOS和PMOS晶体管的组合被称为CMOS晶体管。实现的不同逻辑门和其他数字逻辑器件必须具有PMOS逻辑。这项技术价格低廉,抗干扰能力强。本文讨论了一种MOS晶体管,如PMOS晶体管。

什么是PMOS晶体管?

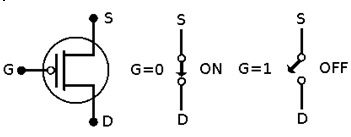

PMOS晶体管或P沟道金属氧化物半导体是一种在沟道或栅极区域中使用P型掺杂剂的晶体管。这个晶体管与NMOS晶体管正好相反。这些晶体管有三个主端子;源极、栅极和漏极,其中晶体管的源极设计为p型衬底,漏极端子设计为n型衬底。在这个晶体管中,像空穴一样的电荷载流子负责电流的传导。PMOS晶体管符号如下所示。

PMOS晶体管是如何工作的?

工作的p型晶体管与n型晶体管完全相反。每当晶体管获得不可忽略的电压时,它就会形成开路,这意味着没有从栅极(G)端子到源极(S)的电流。类似地,当该晶体管获得大约0伏的电压时,它形成闭合电路,这意味着电流从栅极(G)端子流到漏极(D)。

这个气泡也被称为反转气泡。因此,这个圆圈的主要功能是反转输入电压值。如果栅极端子提供1电压,那么这个反相器将把它变为零,并相应地使电路工作。所以PMOS晶体管和NMOS晶体管的功能完全相反。一旦我们将它们合并为一个MOS电路,那么它将成为一个CMOS(互补金属氧化物半导体)电路。

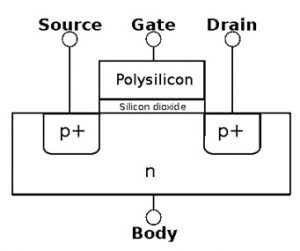

PMOS晶体管的横截面

PMOS晶体管的横截面如下所示。pMOS晶体管由n型体构成,该n型体包括与栅极相邻的两个p型半导体区域。这个晶体管有一个控制栅极,如图所示,它控制两个端子(如源极和漏极)之间的电子流。在pMOS晶体管中,主体被保持在+ve电压。一旦栅极端子为正,则源极端子和漏极端子被反向偏置。一旦发生这种情况,就没有电流流动,因此晶体管将关闭。

一旦栅极端子处的电压供应降低,则正电荷载流子将被吸引到Si-SiO2界面的底部。每当电压变得足够低时,沟道将被反转,并通过允许电流流动来创建从源极端到漏极的传导路径。

每当这些晶体管处理数字逻辑时,通常只有两个不同的值,如1和0(ON和OFF)。晶体管的正电压被称为VDD,它表示数字电路中的逻辑高(1)值。TTL逻辑中的VDD电压电平通常在5V左右。目前,晶体管实际上无法承受如此高的电压,因为它们通常在1.5V至3.3V之间。低电压通常被称为GND或VSS。因此,VSS表示逻辑“0”,并且它也被正常设置为0V。

PMOS晶体管电路

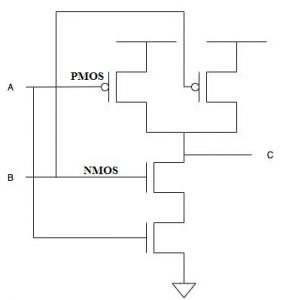

使用PMOS晶体管和NMOS晶体管的NAND栅极设计如下所示。通常,数字电子中的NAND门是一种逻辑门,也称为NOT-AND门。只有当两个输入为高(1)并且其输出是and门的补码时,该门的输出才为低(0)。如果两个输入中的任何一个为LOW(0),则它给出高输出结果。

在下面的逻辑电路中,如果输入A为0,B为0,则pMOS的A输入将产生“1”,nMOS的A输入则产生“0”。因此,该逻辑门生成逻辑“1”,因为它通过闭合电路连接到源极,并通过开路与GND分离。

当A为“0”,B为“1”时,pMOS的A输入将生成“1”,NMOS的A输入则生成“0”。因此,该栅极将产生逻辑1,因为它通过闭合电路连接到源极,并通过开路与GND分离。当A为“1”,B为“0”时,pMOS的“B”输入将产生高输出(1),NMOS的“B’输入将产生低输出(0)。因此,这个逻辑门将产生逻辑1,因为它通过闭合电路连接到源极,并通过开路与GND分离。

当A为'1',B为'1'时,pMOS的A输入将产生零,nMOS的A输入则产生'1'。因此,我们也应该验证pMOS和nMOS的B输入。pMOS的B输入将生成“0”,nMOS的B输入则生成“1”。因此,该逻辑门将生成逻辑“0”,因为它通过开路与源极分离,并通过闭合电路连接到GND。

真值表

下面给出了上述逻辑电路的真值表。

| A. |

B | C |

| 0 |

0 | 1. |

| 0 |

1. | 1. |

| 1. | 0 | 1. |

| 1. | 1. | 0 |

PMOS晶体管的阈值电压通常是“Vgs”,这是创建称为沟道反转的沟道所必需的。在PMOS晶体管中,衬底和源极端简单地连接到“Vdd”。如果我们开始通过参考栅极端子处的源极端子将电压从Vdd降低到您注意到沟道反转的点,在这个位置,如果您分析Vgs和源极处于高电位,那么您将得到负值。因此,PMOS晶体管具有负的Vth值。

PMOS制造工艺

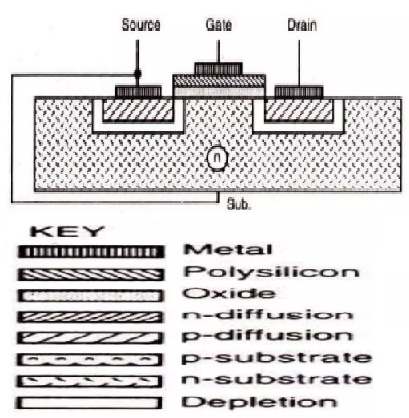

下面将讨论PMOS晶体管制造中涉及的步骤。

第1步:

通过简单地掺杂磷材料,将薄硅晶片层转变为N型材料。

第2步:

在完整的p型衬底上生长厚的二氧化硅(Sio2)层。

第3步:

现在,表面在厚厚的二氧化硅层上涂上了光致抗蚀剂。

第4步:

之后,通过掩模将该层简单地暴露于UV光,该掩模限定了将与晶体管沟道一起发生扩散的那些区域。

步骤5:

这些区域与下面的二氧化硅相互蚀刻掉,使得晶片的表面暴露在由掩模限定的窗口内。

第6步:

分离剩余的光致抗蚀剂,并在芯片的整个表面上生长通常0.1微米的薄Sio2层。之后,在其上放置多晶硅以形成栅极的结构。将光致抗蚀剂放置在整个多晶硅层上,并通过掩模2暴露UV光。

步骤7:

扩散是通过将晶片加热到最高温度并使含有所需p型杂质(如硼)的气体通过来实现的。

第8步:

生长1微米厚的二氧化硅,并在其上沉积光刻胶材料。在栅极、源极和漏极的首选区域用掩模3暴露紫外线,这些区域被蚀刻以形成接触切口。

步骤9:

现在,金属或铝被沉积在其1微米厚的表面上。再次,在整个金属上生长光致抗蚀剂材料,并通过掩模4暴露UV光,掩模4被蚀刻以形成所需的互连设计。最终的PMOS结构如下所示。

PMOS晶体管特性

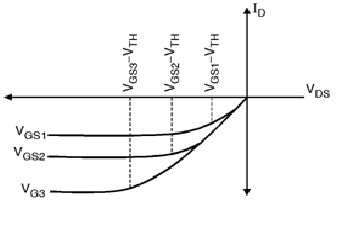

PMOS晶体管的I-V特性如下所示。这些特性被划分为两个区域,以便获得漏极到源极电流(I DS)及其端子电压(如线性和饱和区域)之间的关系。

在线性区域中,当VDS(漏极到源极电压)增加时,IDS将线性增加,而在饱和区域中,I DS是稳定的&它与VDS无关。ISD(源极到漏极电流)及其端子电压之间的主要关系是通过NMOS晶体管的类似程序得出的。在这种情况下,唯一的变化将是存在于反转层内的电荷载流子仅仅是空穴。当空穴从源极移动到漏极时,电流的流动也是相同的。

因此,负号出现在当前方程式中。此外,在器件的端子处施加的所有偏置都是负的。因此,PMOS晶体管的ID–VDS特性如下所示。

线性区域中PMOS晶体管的漏极电流方程如下所示:

ID=–mp考克斯

同样,饱和区域中PMOS晶体管的漏极电流方程如下:

ID=–mp考克斯(VSG–|V TH|p)^2

其中“mp”是空穴的迁移率,“|VTH|p”是PMOS晶体管的阈值电压。

在上面的等式中,负号表示ID(漏极电流)从漏极(D)流向源极(S),而空穴沿相反方向流动。当空穴的迁移率与电子迁移率相比较低时,PMOS晶体管受到低电流驱动的能力的影响。

因此,这一切都是关于PMOS晶体管或p型mos晶体管的概述——制造、电路及其工作。PMOS晶体管设计有p源极、n衬底和漏极。PMOS的载流子是空穴。一旦在栅极端子处施加低电压,该晶体管就导通。与NMOS器件相比,基于PMOS的器件不太容易受到干扰。这些晶体管可以用作电压控制电阻器、有源负载、电流镜、跨阻抗放大器,也可以用于开关和电压放大器。这里有一个问题要问你,什么是NMOS晶体管?