简单的分析产生更好的设计结果

用统计方法回答“我的示意图是否适合给定的PCB区域?”和“布局需要多长时间?”。 当原理图完成时,所有工程师面临的情况是“我的原理图是否适合给定的PCB区域?”和“布局需要多长时间?” 几十年来,我一直面临着同样的问题,大约10年前,我终于...

用统计方法回答“我的示意图是否适合给定的PCB区域?”和“布局需要多长时间?”。

当原理图完成时,所有工程师面临的情况是“我的原理图是否适合给定的PCB区域?”和“布局需要多长时间?”

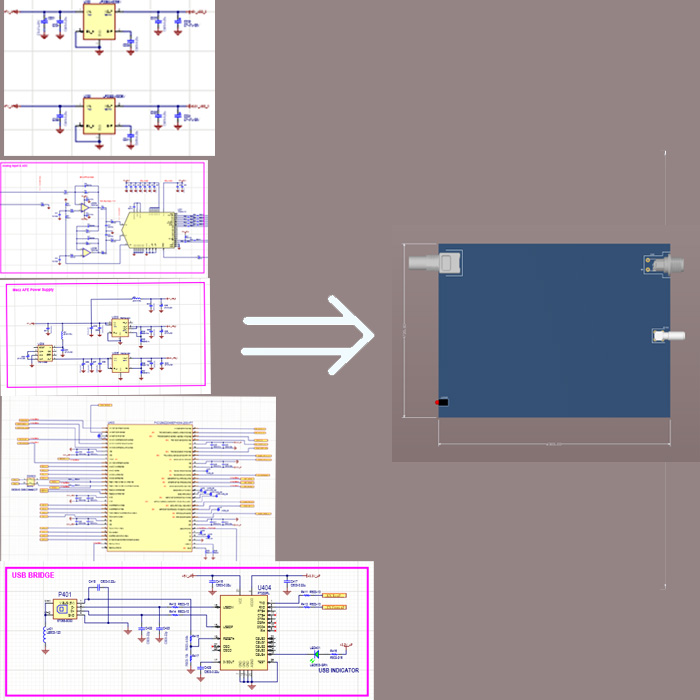

几十年来,我一直面临着同样的问题,大约10年前,我终于有时间对这个问题采取统计方法[1]。这涉及到编写一个脚本,该脚本采用原理图物料清单(BOM),包括所有零件区域、零件引脚和设计中每个零件的数量。然后,这个脚本给我一个封装外形到PCB利用率区域的输出,并输出PCB利用率和要布线的引脚数量(图1)。

过去曾报道过一些(非常少的)PCB估计尝试,其中一些方法使用更复杂的标准作为其估计量的输入。我在“方差分析”[2]方面的训练教会了我“保持简单”,并首先从(可能的)最重要的事情开始。基于我做得最多的工作类型,该零件的PCB面积和设计中的引脚总数对我来说似乎是一个良好的开端。

<img data-lazy-fallback="1" decoding="async" src="https://uploads.9icnet.com/images/aritcle/20230421/figure1.jpg" alt="">

图1:一个示意图和一块空白板,任何设计师面临的问题都是:“它适合吗?”。资料来源:史蒂夫·哈格曼

我的典型设计分析

我做了很多基带模拟和射频设计,但这些设计总是有某种逻辑控制,无论是锁存器到更复杂的控制FPGA或微处理器,所以一切都是混合信号设计。虽然我可能需要长度匹配一些痕迹,但这在我的设计中所占的比例并不大。RF迹线比基带信号需要更长的布局时间,但我在一阶分析中没有将它们分开。

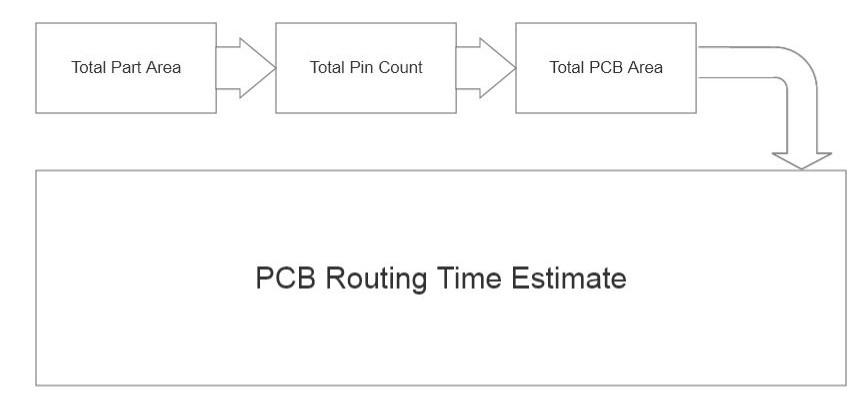

即使原理图不完整,如果你只是根据经验绘制框图,也可以对所需的零件做出合理的估计。今天,当您可以查看无数的参考设计并计算它们所需的部件时,情况尤其如此(图2)。这比一些疯狂的猜测好1000%,而这些猜测往往很低。

<img data-lazy-fallback="1" decoding="async" src="https://uploads.9icnet.com/images/aritcle/20230421/figure2.jpg" alt="">

图2:对总零件面积、总PCB面积和引脚数量的简单分析可以为图1中提出的问题提供简单的答案。资料来源:史蒂夫·哈格曼

分析结果

在接下来的10个左右的PCB设计过程中,我有足够的信息开始理解数据。第一个有趣的点是提前很好地了解零件与PCB面积的比例,而不是猜测。这直接导致了解所需的层数和所需的技术。当然,大量的射频电路也将通过所需的技术驱动PCB。随着PCB密度的增加,增加布线层使布线工作变得更容易,如果设计开始变得非常密集,那么使用过孔技术(如焊盘中过孔)也有助于布线。

起初,我想我可能不得不将基带和射频设计分解为不同的估计,但一个非常有趣的事实出现了。我发现,一个相当密集的PCB的布局时间几乎不取决于我的布线,而是几乎完全由引脚需要路由的。

尽管路由RF迹线比路由基带迹线需要更长的时间,但我发现这是由必须路由的引脚数量驱动的。我发现这是因为基带IC几乎有所有需要布线的引脚,而典型的RF IC有很多接地引脚,这些引脚几乎是由铜层填充自动布线的。这意味着,虽然路由RF迹线需要更长的时间,但典型RF IC上的无数接地引脚弥补了这一点,并且在每个部件的基础上,无论我路由什么技术,每个引脚的时间都是相同的。

这产生了一个非常简单的双变量度量:

- 无论是哪种信号,我都需要相同的平均时间来路由每个引脚。

- 如果出现以下情况,则必须进行修改:

- PCB的密度开始变得过高。这是一个指数修饰符。随着密度比的提高,走路线的时间呈指数级增长。

- 对层数、过孔或奇怪的PCB形状等的任何限制都会使设计更难布线。

分析结果让我非常惊讶,因为这一切都归结为设计中的引脚总数,而与所采用的特定技术无关。

我提出了一个指标:开始PCB设计的最低时间为X小时,这包括制作项目,并最终将所有输出文件汇集在一起以构建设计,然后对于0到Z%密度的PCB,每个引脚的分钟数为Y;除了这些限制之外,还需要添加一些修改内容。

最终的估计方程是,

估计时间=X+(Y*Z)

我的X、Y和Z指标适用于我和我通常做的工作;你需要确定这些指标对你自己来说是什么,以及它们是否适用于你的特定工作。

固件/软件应用程序

我通常也会为我的设计编写固件驱动程序层,通过应用上面概述的相同分析原理,我发现编写和测试IC设备驱动程序平均需要T个小时。由于重复使用,或者由于有制造商提供的代码示例,一些设备驱动程序将花费较短的时间,而有些设备驱动程序由于不可预见的问题将花费较长的时间。然而,在任何给定的项目中,这一切都趋于平均。

同样,开启和测试大致相当于验证每个固件驱动程序和每个IC的测试的一定时间。这也将在一个典型项目的过程中实现。

我发现这个结果与其他人在不同学科中发现的结果相似。例如,Allen Holub等人发现,人们可以简单地通过计算用户故事的数量来估计软件项目[3]。我敢打赌,许多看似复杂的人类努力都可以用类似的方式准确估计。但不要只相信之前公布的一些结果,你可能无法跳过数据采集和分析步骤,因为它们会重申你是否走在正确的轨道上,或者没有给你宝贵的见解,让你能够亲自确定它们是否适用于你的特定工作流程。

使用简单的工具来很好地处理事情

在分析完成后,这似乎过于简单和明显,然而,当我开始这个项目时,结果会是什么并不明显。这是将“方差分析”方法[4]应用于任何给定问题以处理流程的另一种情况,无论是设计还是生产。正如我在上一篇关于“管理混乱“,一些非常简单的工具可以在理解和处理事情方面发挥作用。

工具书类

- Hageman,Steve,“估计PCB设计时间和复杂性”,PCB设计007,2011年3月1日

- Hageman,Steve,“管理混乱”,EDN,2023年2月7日。https://www.edn.com/managing-chaos/

- Holub,Allen,“无估计”,2015年7月5日。https://www.youtube.com/watch?v=QVBlnCTu9Ms

- 唐纳德·惠勒,“理解变异:管理混乱的关键”,1993年,SPC出版社,田纳西州诺克斯维尔,国际标准图书编号:0-945320-35-3

>>这篇文章最初发表在我们的姐妹网站上,电子数据网络.

<img data-lazy-fallback="1" decoding="async" alt="" style="width: 110px; float: left; margin: 0px 4px 0px 0px;" src="https://uploads.9icnet.com/images/aritcle/20230421/contrib-Steve-Hageman-.jpg">

史蒂夫·哈格曼大约从五年级开始就被确认为“模拟疯狂”。他有幸设计运算放大器、开关电源、千兆赫采样示波器、锁定放大器、无线电接收器、50 GHz射频电路以及数字无线产品的测试设备。Steve知道所有的现代设计都不可能用Rs、Ls和Cs来完成,所以他涉猎了PC和嵌入式系统的编程,足以完成这项工作。