MPC860CPX667LB集成了PowerPC™ 基于Power Architecture构建的处理器核心™ 具有网络、电信和无线基础设施应用所需的系统逻辑的技术。MPC860CPX667LB是PowerQUIC的成员™ III系列设备,将对行业标准接口的系统级支持与实现Power Architecture技术嵌入式类别的处理器相结合。有关处理器的功能特性,请参阅MPC8560 PowerQUICC III集成通信处理器参考手册。

要查找此文档的任何已发布勘误表或更新,请联系您的Freescale销售办公室。

特色

- 32位、双问题、超标量、七级流水线

- 850 MIPS,800 MHz(预计为2.1节)

- 支持行锁定的32 KB L1数据和32 KB L1指令缓存

- 256 KB片上二级缓存,具有直接映射功能

- 增强的硬件和软件调试支持

- 内存管理单元(MMU)

- 单精度浮点SIMD扩展

- 高性能RISC CPM,最高支持333 MHz

- CPM软件与先前系列的兼容性

- 大于1 Gbps的CPM总带宽

- 32 KB双端口RAM

- 128 KB ROM+32 KB RAM,用于协议微码存储

- 两个UTOPIA II级主/从端口,支持多PHY(一个可以是16位)

- 三个MII接口

- 八个TDM接口(T1/E1),两个可与T3/E3接口的TDM端口

- 四个SCC支持HDLC和SDLC、HDLC总线、UART、透明、BISYNC

- 三个FC支持:

- 高达155 Mbps ATM SAR-AAL0、AAL1、AAL2、AAL3/4、AAL5

- 10/100 Mbps以太网(最多三个)IEEE®802.3X

- 45 Mbps HDLC/透明(最多三个)

- 两个MCC,每个MCC支持128条全双工、64 kbps、HDLC线路,共256个信道

- ATM传输汇聚层能力(8信道)

- ATM(IMA)功能的集成反复用

- 两个三倍速以太网控制器(TSEC),支持10/100/1000 Mbps以太网(符合IEEE 802.3、802.3u、802.3x、802.3z和802.3ac),带有两个GMII/TBI/RGMII接口

- 166 MHz,64位,2.5V I/O,DDR SDRAM内存控制器,完全支持ECC

- 500 MHz,8位,LVDS I/O,RapidIO控制器

- 133 MHz,64位,3.3V I/O,PCI-X 1.0a/PCI 2.2总线控制器

- 166 MHz,32位,3.3V I/O,带内存控制器的本地总线

- 集成四通道DMA控制器

- 中断控制器

- IEEE 1149.1 JTAG测试访问端口

- 1.2V核心电源,带3.3V和2.5V I/O

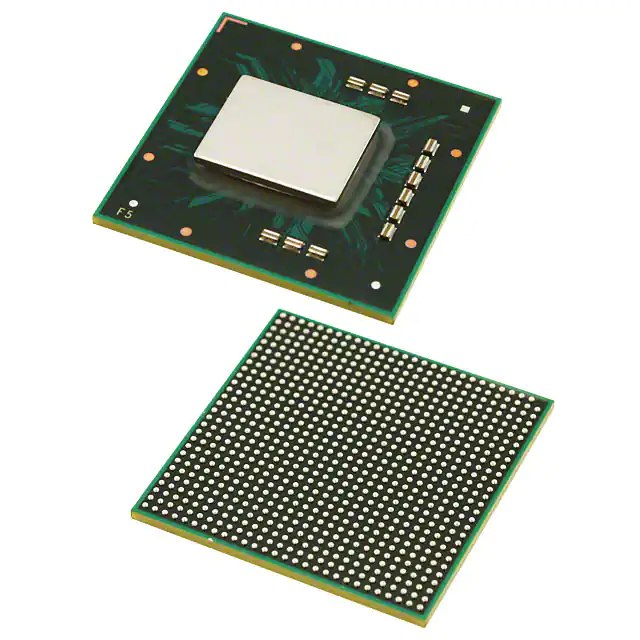

- 783针FC-BGA封装

- 该产品包含在NXP®的产品寿命计划中,在推出后至少可保证10年的供应