描述

MAX 7000A(包括MAX 7000AE)设备是基于Altera第二代MAX的高密度、高性能设备

建筑学基于EEPROM的MAX 7000A器件采用先进的CMOS技术制造,工作电压为3.3V,可提供600至10000个可用的栅极、ISP、快至4.5ns的引脚到引脚延迟和高达227.3MHz的计数器速度。-4、-5、-6、-7和某些-10速度等级的MAX 7000A设备与PCI特殊兴趣组(PCI SIG)PCI本地总线规范2.2版33 MHz操作的时序要求兼容。

特征

■基于第二代多阵列矩阵的高性能3.3-VEEPROM可编程逻辑器件(PLD)

(MAX)架构(见表1)

■3.3V系统内可编程性(ISP),通过内置IEEE Std.1149.1联合测试行动组JTAG接口,具有先进的引脚锁定功能

-符合IEEE标准1532的系统可编程(ISP)电路MAX7000AE器件

-EPM7128A和EPM7256AET144-7设备ISP电路与IEEE标准1532兼容

■符合IEEE标准1149.1的内置边界扫描测试(BST)电路

■ 支持JEDEC Jam标准测试和编程语言

(镫骨)JESD-71

■增强的ISP功能

-用于更快编程的增强ISP算法(不包括EPM7128A和EPM7256AET144-7设备)

-确保完整编程的ISP_Done位(不包括EPM7128A和EPM7256AETI144-7设备)

-在系统内编程期间,上拉I/O引脚上的电阻器

■引脚与流行的5.0-V MAX7000S设备兼容

■从600到10000个可用门的高密度PLD

■扩展温度范围

特色

■ 通过内置的IEEE标准1149.1联合测试行动组(JTAG)接口实现3.3V系统内可编程性(ISP),具有先进的引脚锁定功能

–符合IEEE标准1532的系统可编程性(ISP)电路中的MAX 7000AE设备

–EPM7128A和EPM7256A设备ISP电路与IEEE标准1532兼容

■ 符合IEEE标准1149.1的内置边界扫描测试(BST)电路

■ 支持JEDEC Jam标准测试和编程语言(STAPL)JESD-71

■ 增强的ISP功能–增强的ISP算法可实现更快的编程(不包括EPM7128A和EPM7256A设备)

–ISP_Done位以确保完整编程(不包括EPM7128A和EPM7256A设备)

–在系统内编程期间,上拉I/O引脚上的电阻器

■ 引脚与流行的5.0-V MAX 7000S设备兼容

■ 从600到10000个可用门的高密度PLD

■ 扩展温度范围

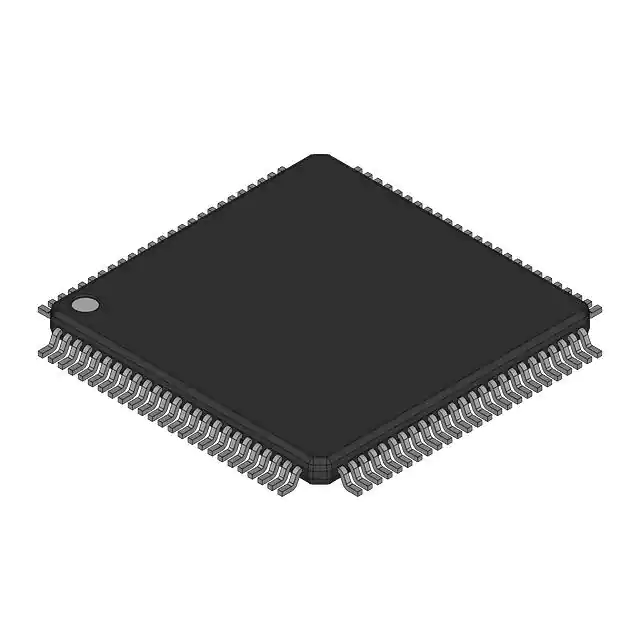

(图片:引线/示意图)